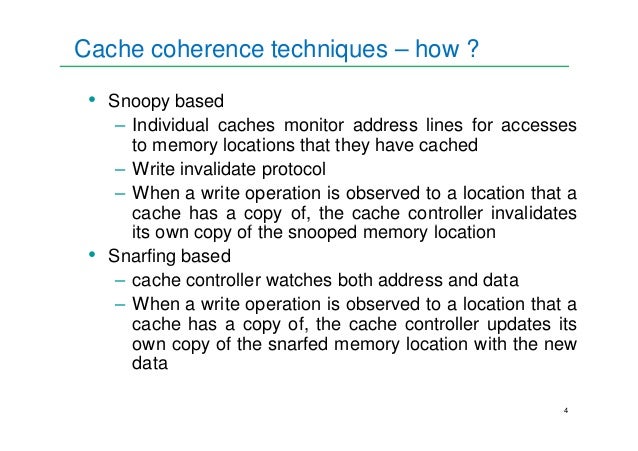

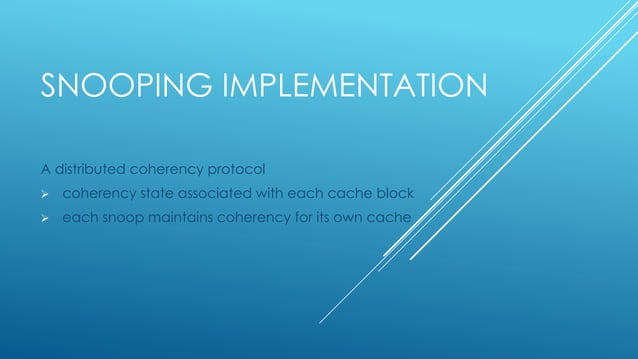

This definition is incomplete because it lacks important and essential information as the actions that these produce. These protocols are generally classified based only on the cache states (from 3 to 5 and 7 or more) and the transactions between them, but this could create some confusion. Various cache-coherency protocols are used to maintain data coherency between caches. In a snooping system, all the caches monitor (or snoop) the bus transactions to intercept the data and determine if they have a copy on its cache. Usually in SMP the coherency is based on the "Bus watching" or " Snoopy" (after the Peanuts' character Snoopy ) approach.

The protocols to maintain the coherency for multiple processors are called cache-coherency protocols. A data consistency problem may occur when a data is modified in one cache only. In multiprocessor systems with separate caches that share a common memory, a same datum can be stored in more than one cache.

The traffic can reduced by using a cache that acts as a "filter" versus the shared memory, that is the cache is an essential element for shared-memory in SMP systems. Bandwidth can be increasing by using large data bus path, data crossbar, memory interleaving (multi-bank parallel access) and out of order data transaction. The bottleneck of these systems is the traffic and the Memory bandwidth. The connection is made using a System Bus or a Crossbar ("xbar") or a mix of two previously approach, bus for address and crossbar for Data (Data crossbar). Systems operating under a single OS ( Operating System) with two or more homogeneous processors and with a centralized shared Main Memory SMP – Symmetric Multiprocessor SystemĮach processor has its own cache that acts as a bridge between processor and Main Memory. Protocol used in bus-based systems like a SMP systems

#Cache coherence vs consistency update#

Update all the copies on other caches (write-broadcasting), while the memory may be updated (write through) or not updated (write-back).Invalidate all the copies on other caches (broadcast-invalidate).This problem arises when a data is modified in one cache. In systems as Multiprocessor system, multi-core and NUMA system, where a dedicated cache for each processor, core or node is used, a consistency problem may occur when a same data is stored in more than one cache. At the moment the main protocols used are the R-MESI type / MESIF protocols and the HRT-ST-MESI (MOESI type) or a subset or an extension of these. Many of the following protocols have only historical value. They are shown directly on the new state. For simplicity, all " miss" Read and Write status transactions which obviously come from state " I" (or miss of Tag), in the diagrams are not shown. ( March 2020)Įxamples of coherency protocols for cache memory are listed here. This article may need to be rewritten to comply with Wikipedia's quality standards.

0 kommentar(er)

0 kommentar(er)